[10:57 Mon,17.January 2022 by Thomas Richter] |

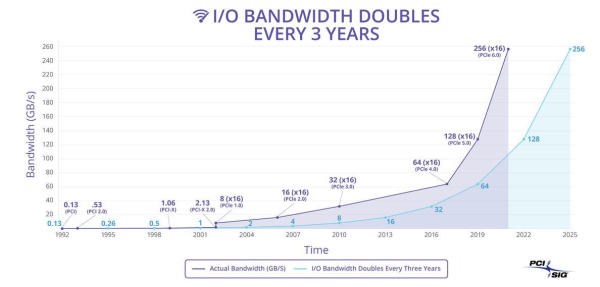

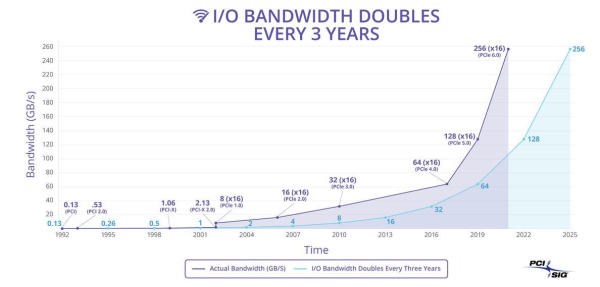

With Intel&s PCIe 6.0 doubles speed.And as the first just-introduced NVMe SSDs show, a larger bandwidth is indeed necessary soon, the  Development of the speed of the PCIe versions PCIe 3.0, 4.0, 5.0 and 6.0 in comparisonAfter nearly 10 years of PCIe 3.0, the PCI-SIG is now making good on its resolution to present a brisker pace of development and aim for a doubling of PCIe bandwidth approximately every 3 years. With PCIe 6.0 it will then be 128 GB/s in one direction or 256 GB/s in two directions per x16 slot, i.e. 8 GB/s per lane. For comparison: PCIe 3.0 achieves a maximum of 1 GB/s per lane (16 GB/s for x16), the current PCIe 4.0 a maximum of 2 GB/s per lane (or 32 GB/s for an x16 slot with 16 lanes) and the now upcoming PCIe 5.0 4 GB/s (x16: 64 GB/s).  Development of the speed of the PCIe versions PCIe 6.0 will have low latency,be backward compatible with previous versions, and use PAM-4 (Pulse Amplitude Modulation with 4 stages) coding and low-latency Forward Error Correction (FEC) with additional mechanisms to improve bandwidth efficiency. The PCIe Bus.The PCIe bus is the backbone of a PC&s data flow; the CPU uses it to communicate with the graphics card, mass storage devices such as SSDs and hard disks, and other cards connected to it (such as capture cards), among others. The higher speed per lane allows faster transfers over the PCIe bus or, because of the higher bandwidth, the use of fewer lanes for a task. §PIC&2§:Speeds of the PCIe versions in comparison Although the new PCIe versions are mainly aimed at the very bandwidth-hungry server market, a high bandwidth is always good news for video editing (especially of higher resolution formats like 6K, 8K as well as RAW) as it can avoid possible bottlenecks during work - be it when transferring data to and from an NVMe SSD or when using (multiple) GPUs to calculate effects. The M.2 SSD format often reaches its maximum transfer speed nowadays, since NVMe M.2 SSDs are only connected to the system via four PCIe lanes. However, it will still take 12-18 months until the first hardware - above all CPUs and motherboards as a basic requirement, of course - with PCIe 6.0 are on the market. Bild zur Newsmeldung:

deutsche Version dieser Seite: PCIe 6.0 finalisiert: Doppelte Geschwindigkeit mit bis zu 128 GB/s für x16 Slot |